**The AD9554BCPZ: A High-Performance Quad PLL Clock Translator for Multi-Rate Applications**

In the realm of modern high-speed communication, data acquisition, and digital signal processing systems, the demand for precise and flexible clock management is paramount. The **AD9554BCPZ** from Analog Devices stands out as a sophisticated solution, engineered to address the complex timing requirements of multi-rate applications. This integrated circuit is a **quad PLL clock translator** that excels in generating multiple, independent output clocks from a single or multiple input references, ensuring robust performance across diverse and demanding environments.

At its core, the device features four phase-locked loops (PLLs), each capable of being individually configured. This architecture allows it to **synchronize and translate** input clock frequencies to a wide range of output frequencies with exceptional accuracy. The inputs can accept common reference frequencies from crystals, oscillators, or data stream clocks, while the outputs provide low-jitter, high-stability clocks critical for system timing. A key strength of the AD9554BCPZ is its ability to handle **asynchronous frequency domains**, making it indispensable in systems where different subsystems or line cards operate at varying data rates, such as in telecommunications infrastructure, network switches, and professional video broadcast equipment.

The device is designed for high performance and reliability. It incorporates a **fractional-N frequency synthesizer** in each PLL, enabling very fine frequency resolution and minimizing phase error. This is crucial for meeting the strict jitter specifications of high-speed SerDes (Serializer/Deserializer) interfaces like 10G/40G/100G Ethernet, OTN, and Fibre Channel. Moreover, the AD9554BCPZ offers advanced features such as hitless reference switching and holdover mode. These capabilities ensure continuous operation without phase interruptions if a primary reference fails, automatically switching to a backup source or maintaining output frequency stability based on historical data.

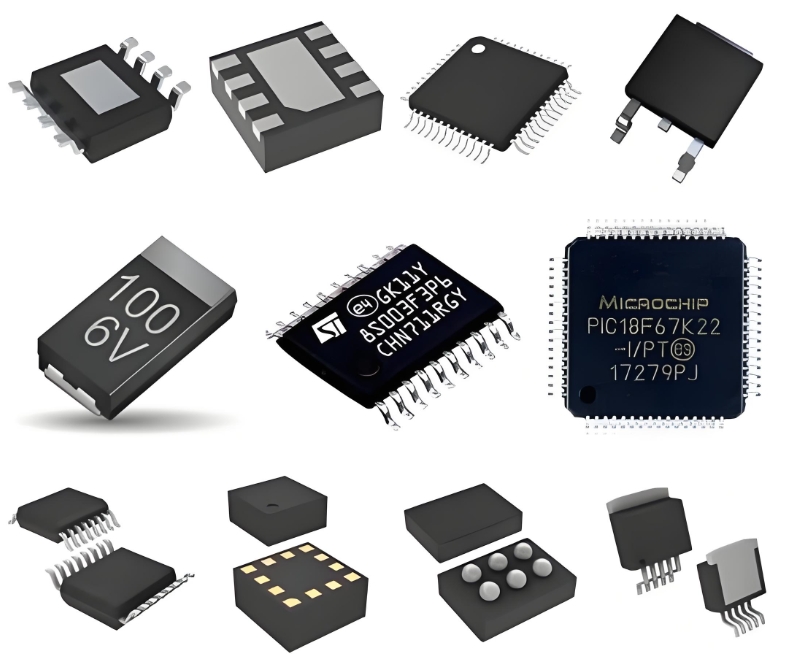

Programming and monitoring the AD9554BCPZ are streamlined through a serial peripheral interface (SPI), allowing for in-system customization of PLL bandwidth, output divider ratios, and other parameters. Its compact 32-lead LFCSP (Lead Frame Chip Scale Package) makes it suitable for space-constrained applications without compromising thermal performance.

**ICGOOODFIND**: The AD9554BCPZ is a superior choice for designers seeking a highly integrated, flexible, and low-jitter clock solution. Its quad PLL architecture provides unparalleled capability for managing multiple clock domains within a single device, simplifying board design and enhancing overall system timing integrity.

**Keywords**: Clock Translation, Phase-Locked Loop (PLL), Jitter Attenuation, Frequency Synthesizer, Multi-Rate Synchronization.